library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

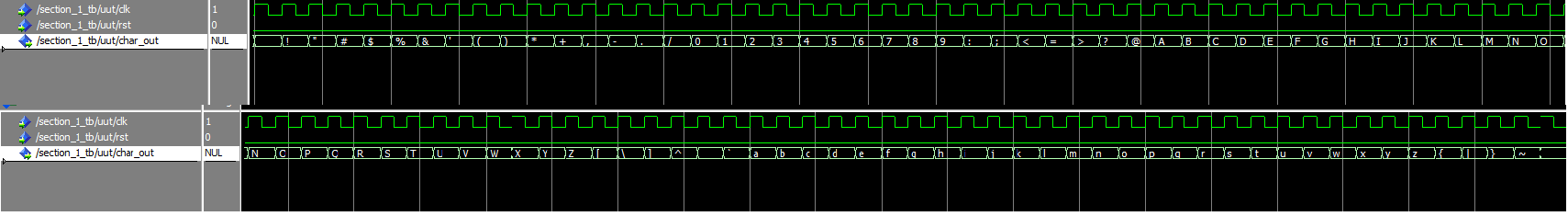

entity section_1 is

port ( clk : in std_logic;

rst : in std_logic;

char_out : out character);

end entity;

architecture behaviour of section_1 is

signal count : integer range 0 to 140;

signal char_out_s : character;

begin

— basic counter

process (clk)

begin

if (rising_edge (clk)) then

if ((count = 0) or (count < 139)) then

count <= count + 1;

elsif (count = 140) then

count <= 0;

end if;

end if;

end process;

— VHDL character set

process (clk)

begin

if (rising_edge (clk)) then

case count is

when 32 => char_out_s <= ' '; -- Space

when 33 => char_out_s <= '!'; -- Exclamation mark

when 34 => char_out_s <= '"'; -- " Double quotes (or s

when 35 => char_out_s <= '#'; -- Number

when 36 => char_out_s <= '$'; -- Dollar

when 37 => char_out_s <= '%'; -- Per cent sign

when 38 => char_out_s <= '&'; -- & Ampersand

when 39 => char_out_s <= '''; -- Single quote

when 40 => char_out_s <= '('; -- Open parenthesis (or open b

when 41 => char_out_s <= ')'; -- Close parenthesis (or close

when 42 => char_out_s <= '*'; -- Asterisk

when 43 => char_out_s <= '+'; -- Plus

when 44 => char_out_s <= ','; -- Comma

when 45 => char_out_s <= '-'; -- Hyphen

when 46 => char_out_s <= '.'; -- Period, dot or full stop

when 47 => char_out_s <= '/'; -- Slash or divide

when 48 => char_out_s <= '0'; -- Zero

when 49 => char_out_s <= '1'; -- one

when 50 => char_out_s <= '2'; -- Two

when 51 => char_out_s <= '3'; -- Three

when 52 => char_out_s <= '4'; -- Four

when 53 => char_out_s <= '5'; -- Five

when 54 => char_out_s <= '6'; -- Six

when 55 => char_out_s <= '7'; -- Seven

when 56 => char_out_s <= '8'; -- Eight

when 57 => char_out_s <= '9'; -- Nine

when 58 => char_out_s <= ':'; -- Colon

when 59 => char_out_s <= ';'; -- Semicolon

when 60 => char_out_s <= '<'; -- < Less than (or open

when 61 => char_out_s <= '='; -- Equals

when 62 => char_out_s <= '>'; -- > Greater than (or cl

when 63 => char_out_s <= '?'; -- Question mark

when 64 => char_out_s <= '@'; -- At symbol

when 65 => char_out_s <= 'A'; -- Uppercase A

when 66 => char_out_s <= 'B'; -- Uppercase B

when 67 => char_out_s <= 'C'; -- Uppercase C

when 68 => char_out_s <= 'D'; -- Uppercase D

when 69 => char_out_s <= 'E'; -- Uppercase E

when 70 => char_out_s <= 'F'; -- Uppercase F

when 71 => char_out_s <= 'G'; -- Uppercase G

when 72 => char_out_s <= 'H'; -- Uppercase H

when 73 => char_out_s <= 'I'; -- Uppercase I

when 74 => char_out_s <= 'J'; -- Uppercase J

when 75 => char_out_s <= 'K'; -- Uppercase K

when 76 => char_out_s <= 'L'; -- Uppercase L

when 77 => char_out_s <= 'M'; -- Uppercase M

when 78 => char_out_s <= 'N'; -- Uppercase N

when 79 => char_out_s <= 'O'; -- Uppercase O

when 80 => char_out_s <= 'P'; -- Uppercase P

when 81 => char_out_s <= 'Q'; -- Uppercase Q

when 82 => char_out_s <= 'R'; -- Uppercase R

when 83 => char_out_s <= 'S'; -- Uppercase S

when 84 => char_out_s <= 'T'; -- Uppercase T

when 85 => char_out_s <= 'U'; -- Uppercase U

when 86 => char_out_s <= 'V'; -- Uppercase V

when 87 => char_out_s <= 'W'; -- Uppercase W

when 88 => char_out_s <= 'X'; -- Uppercase X

when 89 => char_out_s <= 'Y'; -- Uppercase Y

when 90 => char_out_s <= 'Z'; -- Uppercase Z

when 91 => char_out_s <= '['; -- Opening bracket

when 92 => char_out_s <= '\'; -- Backslash

when 93 => char_out_s <= ']'; -- Closing bracket

when 94 => char_out_s <= '^'; -- Caret - circumflex

when 95 => char_out_s <= '_'; -- Underscore

when 96 => char_out_s <= '`'; -- Grave accent

when 97 => char_out_s <= 'a'; -- Lowercase a

when 98 => char_out_s <= 'b'; -- Lowercase b

when 99 => char_out_s <= 'c'; -- Lowercase c

when 100 => char_out_s <= 'd'; -- Lowercase d

when 101 => char_out_s <= 'e'; -- Lowercase e

when 102 => char_out_s <= 'f'; -- Lowercase f

when 103 => char_out_s <= 'g'; -- Lowercase g

when 104 => char_out_s <= 'h'; -- Lowercase h

when 105 => char_out_s <= 'i'; -- Lowercase i

when 106 => char_out_s <= 'j'; -- Lowercase j

when 107 => char_out_s <= 'k'; -- Lowercase k

when 108 => char_out_s <= 'l'; -- Lowercase l

when 109 => char_out_s <= 'm'; -- Lowercase m

when 110 => char_out_s <= 'n'; -- Lowercase n

when 111 => char_out_s <= 'o'; -- Lowercase o

when 112 => char_out_s <= 'p'; -- Lowercase p

when 113 => char_out_s <= 'q'; -- Lowercase q

when 114 => char_out_s <= 'r'; -- Lowercase r

when 115 => char_out_s <= 's'; -- Lowercase s

when 116 => char_out_s <= 't'; -- Lowercase t

when 117 => char_out_s <= 'u'; -- Lowercase u

when 118 => char_out_s <= 'v'; -- Lowercase v

when 119 => char_out_s <= 'w'; -- Lowercase w

when 120 => char_out_s <= 'x'; -- Lowercase x

when 121 => char_out_s <= 'y'; -- Lowercase y

when 122 => char_out_s <= 'z'; -- Lowercase z

when 123 => char_out_s <= '{'; -- Opening brace

when 124 => char_out_s <= '|'; -- Vertical bar

when 125 => char_out_s <= '}'; -- Closing brace

when 126 => char_out_s <= '~'; -- Equivalency sign - tilde

when 127 => char_out_s <= ' '; -- Delete

when others => null;

end case;

end if;

end process;

char_out <= char_out_s;

end;